#### CACHE CONTENT DUPLICATION

#### Marios Kleanthous

#### University of Cyprus, 2012

The importance of caches and memory hierarchy has increased over time due to the growing gap between processor and memory performance, and it has become more important in Simultaneous Multithreading processors and Chip-multiprocessors. To cover this memory gap, caches have been the subject of numerous studies aiming to improve their performance as well as their power and area efficiency.

This thesis identifies a new phenomenon in caches that has the potential to improve cache performance and efficiency: the Cache Content Duplication (CCD). CCD occurs when there is a miss for a block in a cache and the entire content of the missed block is already in the cache in a block with a different tag. Caches aware of content-duplication can have lower miss penalty by fetching, on a miss to a duplicate block, directly from the cache instead of accessing lower in the memory hierarchy, and can have lower miss rates by allowing only blocks with unique content to enter a cache.

The usefulness of CCD is also examined at all levels of the memory hierarchy. First, we show that CCD is a frequent phenomenon for instruction caches and that an idealized duplication-detection mechanism for instruction caches has the potential to increase performance of an out-of-order processor, with a 16KB, 8-way, 8 instructions per block instruction cache, often by more than 10% and up to 36%. We also propose CATCH, a hardware mechanism for dynamically detecting CCD for instruction caches. Experimental results for an out-of-order processor show

that a duplication-detection mechanism with a 1.38KB cost captures on average 58% of the CCD's idealized potential.

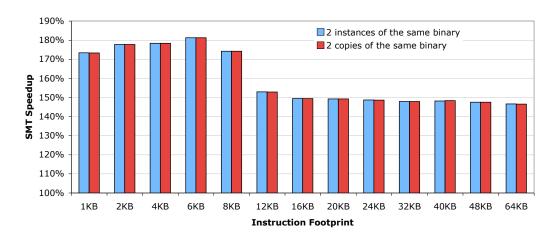

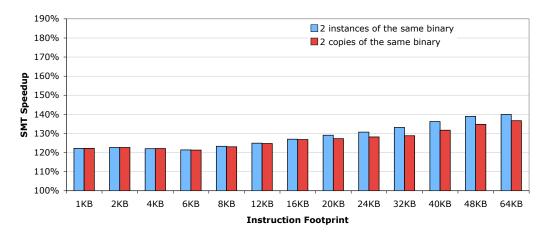

Second, we examine another case of CCD which we call Text Cloning. Text Cloning can occur when running multiple *copies* of the same binary, Extrinsic Text Cloning, or when running multiple *instances* of the same application in a Virtually Indexed Virtually Tagged cache, Intrinsic Text Cloning. Results show that both Intrinsic Text Cloning and Extrinsic Text Cloning can reduce an application's performance. Specifically, Extrinsic Text Cloning causes up to 11% slowdown on existing platforms. Furthermore, we show that CATCH can benefit performance by eliminating the duplication due to Intrinsic Text Cloning and Extrinsic Text Cloning.

Third, we investigate the potential of CCD for L1 data caches. The results indicate that caches exhibit a high amount of dirty blocks thus making the CCD detection and creating stable correlations between different blocks very difficult. If a block is written, all duplicate relations to that block need to be invalidated. Our analysis also shows that zero runs are very frequent in L1 data caches and, therefore, previously proposed zero detection mechanisms can provide good solutions.

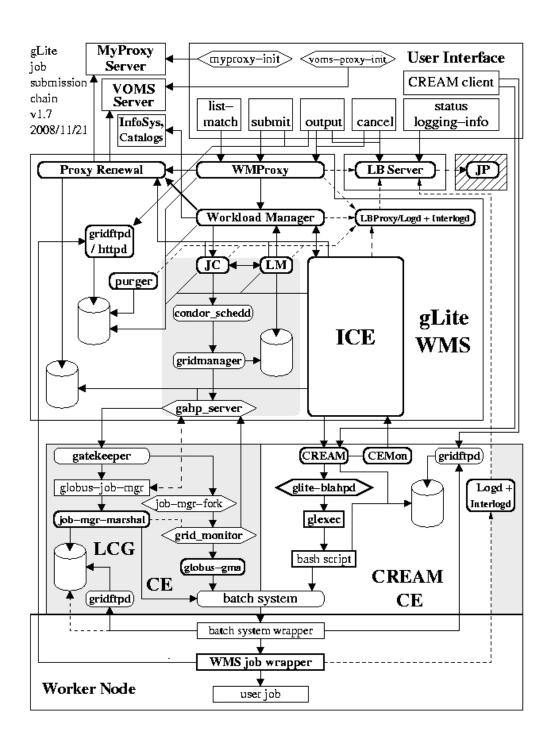

Finally, this thesis considers the CCD phenomenon for Last Level Caches (LLCs). The LLCs are written less frequently (L1 data cache acts as a filter) and have less zero runs because they mostly store evicted cache blocks that have already written with non-zero values. Results indicate that CCD is very frequent for various block granularities, from 4 to 64 bytes, and has potential to improve processors performance or save energy. A new cache design, the Content Duplication Aware Cache, is proposed to detect and eliminate CCD in LLCs. The results indicate that the Content Duplication Aware Cache can improve performance moderately but can reduce Energy Delay product considerably, 10% on average and up to 15% at most, for multiprogram workloads.

Marios Kleanthous – University of Cyprus, 2012

## **CACHE CONTENT DUPLICATION**

### Marios Kleanthous

A Dissertation

Submitted in Partial Fulfillment of the

Requirements for the Degree of

Doctor of Philosophy

at the

University of Cyprus

Recommended for Acceptance

by the Department of Computer Science

April, 2012

© Copyright by

Marios Kleanthous

All Rights Reserved

# **APPROVAL PAGE**

Doctor of Philosophy Dissertation

# CACHE CONTENT DUPLICATION

Presented by

Marios Kleanthous

| Research Supervisor |                       |

|---------------------|-----------------------|

|                     | Yiannakis Sazeides    |

| Committee Member    |                       |

|                     | Pedro Trancoso        |

| Committee Member    |                       |

|                     | Demetrios Zeinalipour |

| Committee Member    |                       |

|                     | Emre Ozer             |

| Committee Member    |                       |

|                     | Andre Seznec          |

University of Cyprus

April, 2012

### ACKNOWLEDGEMENTS

Foremost, I would like to thank my advisor for his support during all the years of my Ph.D. I am deeply grateful for his help, patience, and mostly for his guidance that lead to the completion of this thesis. He taught me how to conduct research and gave me all the tools for a promising future. He has been a great teacher but also a great friend and for that I would like to thank him from the bottom of my heart.

Next, I would like to thank all my Ph.D. committee members for their time and for their punctual comments that helped me improve this thesis. Special thanks also go to all anonymous reviewers that contributed to the development of this thesis over the years.

Also, I would like to thank all my colleagues and friends at the University of Cyprus and Xi-Group for their feedback but also their friendship. Special thanks go to Fanos and Andreas that have been my first colleagues in the lab and still great friends and to Damien for his support and valuable feedback during the last few weeks while preparing my thesis defense.

I am also deeply grateful to my family and especially my parents Michalis and Giannoulla, and my sister Rafaella that stood next to me during all the years of my studies. They have been always there to share the good and the bad moments with me. Also, I would like express my deepest love to my wife, Georgia, for putting up with me all these years and for being always there to support me and encourage me. Without my family and my wife this thesis would have been impossible.

I would also like to thank all my friends outside the University of Cyprus that made my life more interesting during my studies and I believe they will continue to be part of it for many years to come. Especially I would like to thank my best friends Konstantinos, Kyriakos and Telis, and my fishing buddies Giorgos and Christos.

Finally, I would like to dedicated this thesis to all the people that dream for a better world no matter what they face.

# TABLE OF CONTENTS

| Chapter | 1: Introduction                                                               | 1  |

|---------|-------------------------------------------------------------------------------|----|

| 1.1     | Memory Challenges                                                             | 2  |

| 1.2     | Thesis Contributions                                                          | 4  |

| 1.3     | Main Output of this Thesis                                                    | 6  |

| 1.4     | Other Output from this Work                                                   | 7  |

|         | 1.4.1 Improving Branch Prediction by Considering Affectors and Affectees Cor- |    |

|         | relations                                                                     | 7  |

|         | 1.4.2 Entry Replacement Within a Data Store                                   | 7  |

| 1.5     | Thesis Outline                                                                | 8  |

| Chapter | 2: Background and Related Work                                                | 9  |

| 2.1     | Memory Hierarchy Optimizations                                                | 9  |

|         | 2.1.1 Replacement Policies                                                    | 0  |

|         | 2.1.2 Prefetching                                                             | 1  |

|         | 2.1.3 Compression                                                             | 2  |

| 2.2     | Related Work on Compression                                                   | 4  |

|         | 2.2.1 Dynamic Compression                                                     | 5  |

|         | 2.2.2 Static Compression                                                      | 8  |

| 2.3     | Code Compaction                                                               | 8  |

| 2.4     | Dynamic VS Static Techniques and Mechanisms                                   | 9  |

| 2.5     | Cache Content Duplication (CCD)                                               | :0 |

| Chapter | · 3: Methodology 2                                                            | 24 |

| 3.1     | Metric                                                                            | S                                                                                                                                                                                                                                                                                                | 24                                                                                     |

|---------|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| 3.2     | Simula                                                                            | tion Infrastructure                                                                                                                                                                                                                                                                              | 26                                                                                     |

|         | 3.2.1                                                                             | Simulator and Extensions                                                                                                                                                                                                                                                                         | 26                                                                                     |

|         | 3.2.2                                                                             | Single Core Configuration                                                                                                                                                                                                                                                                        | 26                                                                                     |

|         | 3.2.3                                                                             | Multi Core Configuration                                                                                                                                                                                                                                                                         | 27                                                                                     |

| 3.3     | Benchi                                                                            | marks and Characterization                                                                                                                                                                                                                                                                       | 28                                                                                     |

|         | 3.3.1                                                                             | Regions                                                                                                                                                                                                                                                                                          | 28                                                                                     |

|         | 3.3.2                                                                             | SPEC 2000                                                                                                                                                                                                                                                                                        | 29                                                                                     |

|         | 3.3.3                                                                             | ТРС-Н                                                                                                                                                                                                                                                                                            | 29                                                                                     |

|         | 3.3.4                                                                             | Multiprogram Workloads                                                                                                                                                                                                                                                                           | 30                                                                                     |

| Chapter | <b>1</b> •                                                                        | CCD for Instructions                                                                                                                                                                                                                                                                             | 32                                                                                     |

| Спарист |                                                                                   |                                                                                                                                                                                                                                                                                                  |                                                                                        |

|         |                                                                                   |                                                                                                                                                                                                                                                                                                  | 22                                                                                     |

| 4.1     | How to                                                                            | Detect CCD                                                                                                                                                                                                                                                                                       | 33                                                                                     |

| 4.1     | 4.1.1                                                                             | What is the Cache Content Considered for Duplication                                                                                                                                                                                                                                             |                                                                                        |

| 4.1     |                                                                                   |                                                                                                                                                                                                                                                                                                  | 34                                                                                     |

| 4.1     | 4.1.1                                                                             | What is the Cache Content Considered for Duplication                                                                                                                                                                                                                                             | 34<br>35                                                                               |

| 4.1     | 4.1.1<br>4.1.2<br>4.1.3                                                           | What is the Cache Content Considered for Duplication                                                                                                                                                                                                                                             | <ul><li>34</li><li>35</li><li>36</li></ul>                                             |

| 4.2     | 4.1.1<br>4.1.2<br>4.1.3<br>Code F                                                 | What is the Cache Content Considered for Duplication                                                                                                                                                                                                                                             | <ul><li>34</li><li>35</li><li>36</li><li>37</li></ul>                                  |

| 4.2     | 4.1.1<br>4.1.2<br>4.1.3<br>Code F                                                 | What is the Cache Content Considered for Duplication                                                                                                                                                                                                                                             | <ul><li>34</li><li>35</li><li>36</li><li>37</li></ul>                                  |

| 4.2     | <ul><li>4.1.1</li><li>4.1.2</li><li>4.1.3</li><li>Code F</li><li>Limits</li></ul> | What is the Cache Content Considered for Duplication                                                                                                                                                                                                                                             | <ul><li>34</li><li>35</li><li>36</li><li>37</li><li>41</li></ul>                       |

| 4.2     | 4.1.1<br>4.1.2<br>4.1.3<br>Code F<br>Limits<br>4.3.1                              | What is the Cache Content Considered for Duplication                                                                                                                                                                                                                                             | <ul><li>34</li><li>35</li><li>36</li><li>37</li><li>41</li><li>41</li><li>47</li></ul> |

| 4.2     | 4.1.1<br>4.1.2<br>4.1.3<br>Code F<br>Limits<br>4.3.1<br>4.3.2                     | What is the Cache Content Considered for Duplication  When to Learn the Cache Content  Which Sequences are Duplicated  Redundancy Characterization  of Cache-Content-Duplication  CCD in Instruction Caches for Entire Blocks and Valid Blocks  CCD for Basic-Block Caches                       | <ul><li>34</li><li>35</li><li>36</li><li>37</li><li>41</li><li>41</li><li>47</li></ul> |

| 4.2     | 4.1.1<br>4.1.2<br>4.1.3<br>Code F<br>Limits<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4   | What is the Cache Content Considered for Duplication  When to Learn the Cache Content  Which Sequences are Duplicated  Redundancy Characterization  of Cache-Content-Duplication  CCD in Instruction Caches for Entire Blocks and Valid Blocks  CCD for Basic-Block Caches  CCD for Trace Caches | <ul><li>34</li><li>35</li><li>36</li><li>37</li><li>41</li><li>47</li><li>47</li></ul> |

|         | 4.4.2   | Performance Potential of CCD                  | 53        |

|---------|---------|-----------------------------------------------|-----------|

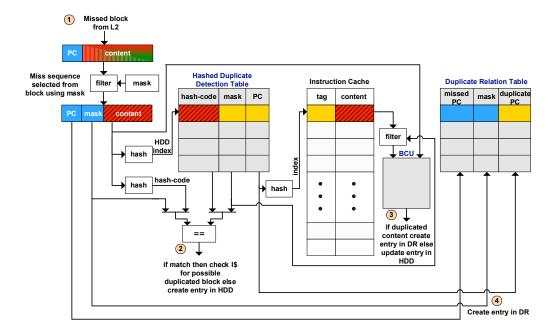

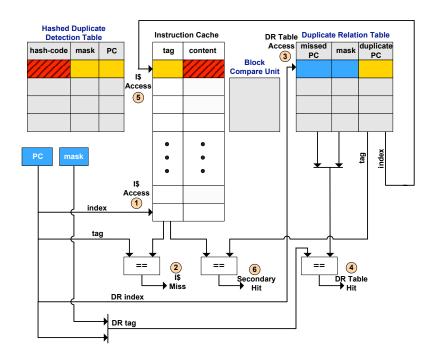

| 4.5     | CATCI   | H: A Method for Dynamically Detecting CCD     | 55        |

|         | 4.5.1   | Hashed-Duplicate-Detection table              | 56        |

|         | 4.5.2   | The Block Compare Unit                        | 58        |

|         | 4.5.3   | Duplicate-Relation table                      | 58        |

|         | 4.5.4   | Allocating and Updating an HDD and a DR entry | 59        |

|         | 4.5.5   | The use of CATCH in DAC and UCC               | 60        |

|         | 4.5.6   | Performance Optimizations                     | 61        |

|         | 4.5.7   | Cost Reduction Optimizations                  | 62        |

|         | 4.5.8   | Pipelining Issues                             | 64        |

| 4.6     | Perform | mance Evaluation of CATCH                     | 65        |

|         | 4.6.1   | CATCH Performance for DAC and UCC Caches      | 66        |

|         | 4.6.2   | CATCH Performance                             | 67        |

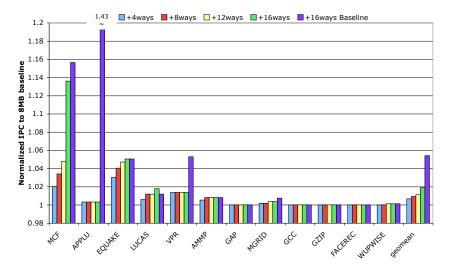

|         | 4.6.3   | Effects of Associativity                      | 69        |

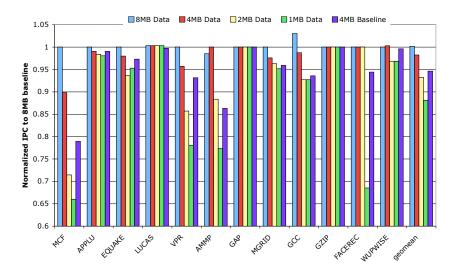

|         | 4.6.4   | Effects of Cache Size                         | 70        |

|         | 4.6.5   | CATCH vs Victim Cache                         | 71        |

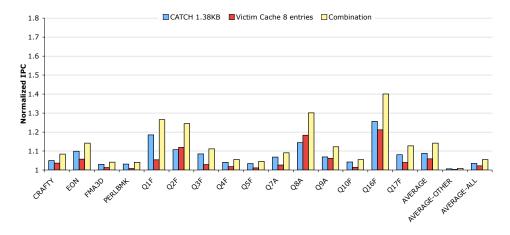

|         | 4.6.6   | Effects of Prefetching                        | 72        |

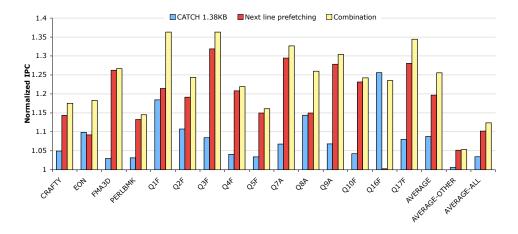

|         | 4.6.7   | Increasing Cache Size                         | 73        |

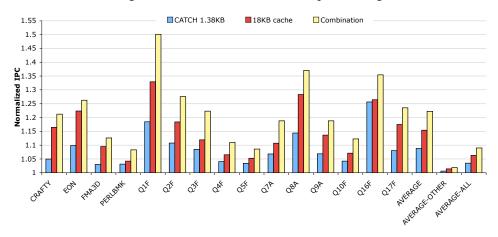

|         | 4.6.8   | CATCH Energy Consumption                      | 74        |

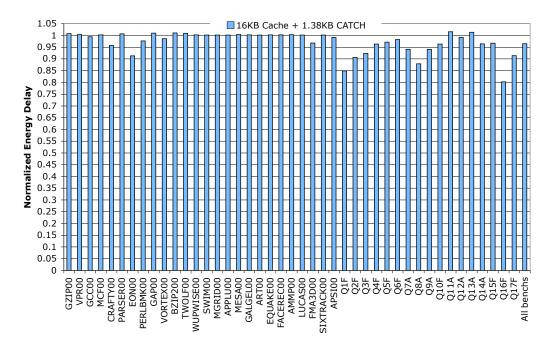

| 4.7     | Chapte  | r Summary                                     | 76        |

| Chapter | 5:      | Extrinsic and Intrinsic Text Cloning          | <b>78</b> |

| 5.1     | Text C  | loning: Causes, Implications and Remedies     | 79        |

|         | 5.1.1   | Extrinsic Text Cloning                        | 79        |

|     |      | 5.1.2   | Intrinsic Text Cloning                           |  |

|-----|------|---------|--------------------------------------------------|--|

|     |      | 5.1.3   | How Important is ETC and ITC                     |  |

|     |      | 5.1.4   | How to Eliminate ETC and ITC                     |  |

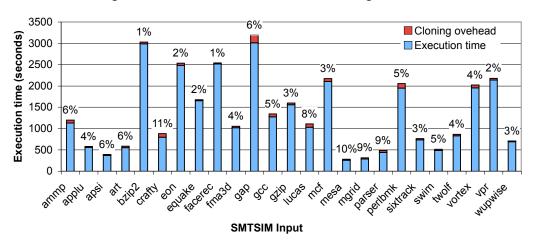

| :   | 5.2  | Grid C  | omputing Systems                                 |  |

|     |      | 5.2.1   | Grid Architecture                                |  |

|     |      | 5.2.2   | Extrinsic Text Cloning in Grid                   |  |

| :   | 5.3  | Evalua  | tion Using Simulation                            |  |

|     |      | 5.3.1   | Results                                          |  |

| :   | 5.4  | Chapte  | r Summary                                        |  |

| Cha | pter | 6:      | CCD for Data 94                                  |  |

|     | 6.1  | Data P  | edundancy Characterization                       |  |

|     |      |         |                                                  |  |

|     | 6.2  | Data D  | uplication Detection                             |  |

|     |      | 6.2.1   | Compressing Dirty Blocks                         |  |

|     |      | 6.2.2   | Compressing Zero Blocks                          |  |

| (   | 6.3  | The Ef  | fects of Duplication Granularity for Data Caches |  |

|     |      | 6.3.1   | Granularity at the Block Level                   |  |

|     |      | 6.3.2   | Granularity at Various Block Segments            |  |

| (   | 6.4  | Chapte  | r Summary                                        |  |

| Cha | pter | 7:      | CCD for Last Level Caches 108                    |  |

| ,   | 7.1  | Single  | Program Workloads                                |  |

|     |      |         |                                                  |  |

| ,   | 7.2  | Multi F | Program Workloads                                |  |

| ,   | 7.3  | Exploit | ting CCD on Last Level Caches                    |  |

|     |      | 731     | Content Dunlication Aware (CDA) Caches           |  |

|          | 7.3.2     | Accessing and Updating a CDA Cache                  | 119 |

|----------|-----------|-----------------------------------------------------|-----|

| 7.4      | Initial l | Results of a CDA Cache                              | 122 |

|          | 7.4.1     | Single Program Workloads                            | 122 |

|          | 7.4.2     | Multi Program Workloads                             | 125 |

| 7.5      | CDA C     | Cache Energy Delay Characterization                 | 130 |

| 7.6      | Implen    | nentation Issues of CDA cache                       | 133 |

| 7.7      | Chapte    | r Summary                                           | 136 |

| Chapter  | 8:        | Conclusions                                         | 138 |

| 8.1      | Contrib   | outions                                             | 138 |

| 8.2      | Future    | Work                                                | 140 |

| Bibliogr | aphy      |                                                     | 142 |

| Appendi  | x A:      | CATCH Design Space Exploration                      | 149 |

| A.1      | HDD I     | Design Space Exploration                            | 149 |

| A.2      | DR De     | sign Space Exploration                              | 149 |

| Appendi  | x B:      | Synthetic Benchmark to Exercises Instruction Caches | 151 |

| Appendi  | x C:      | Acronyms                                            | 153 |

# LIST OF TABLES

| 1 | Summary of related work                                                    |

|---|----------------------------------------------------------------------------|

| 2 | Single Core Baseline Configuration                                         |

| 3 | Multi Core Baseline Configuration                                          |

| 4 | SPEC 2000 Simulated benchmarks                                             |

| 5 | TPC-H Simulated benchmarks                                                 |

| 6 | Energy consumption per access of 16KB 8-way and CATCH                      |

| 7 | Cache and CATCH events and units accessed                                  |

| 8 | Benchmark Classification based on their LLC cache pressure and performance |

|   | potential                                                                  |

# LIST OF FIGURES

| 1  | Memory Gap [1]                                                                     | 2  |

|----|------------------------------------------------------------------------------------|----|

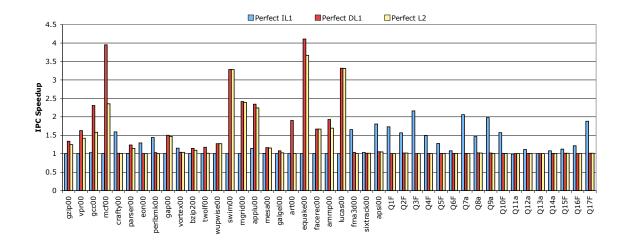

| 2  | Performance improvement of an out-of-order processor with perfect cache            | 2  |

| 3  | Cache Content Duplication (a) Without CCD, (b) With CCD                            | 4  |

| 4  | Valid block masked out from a cache block                                          | 35 |

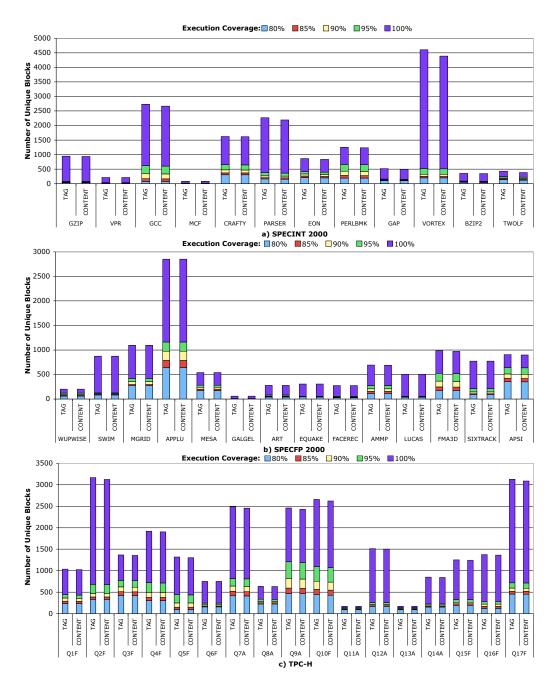

| 5  | Execution coverage of unique blocks for the a) SPECINT 2000, b) SPECFP 2000        |    |

|    | and c) TPC-H benchmarks                                                            | 38 |

| 6  | Execution coverage of unique valid blocks for the a) SPECINT 2000, b) SPECFP       |    |

|    | 2000 and c) TPC-H benchmarks                                                       | 39 |

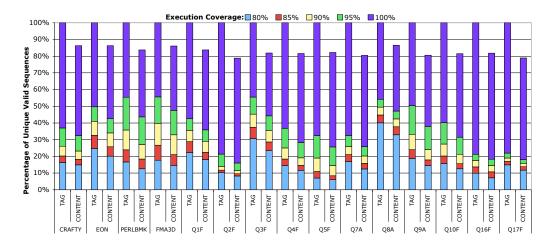

| 7  | Execution coverage breakdown of unique valid blocks in percentages for a se-       |    |

|    | lected subset of benchmarks                                                        | 40 |

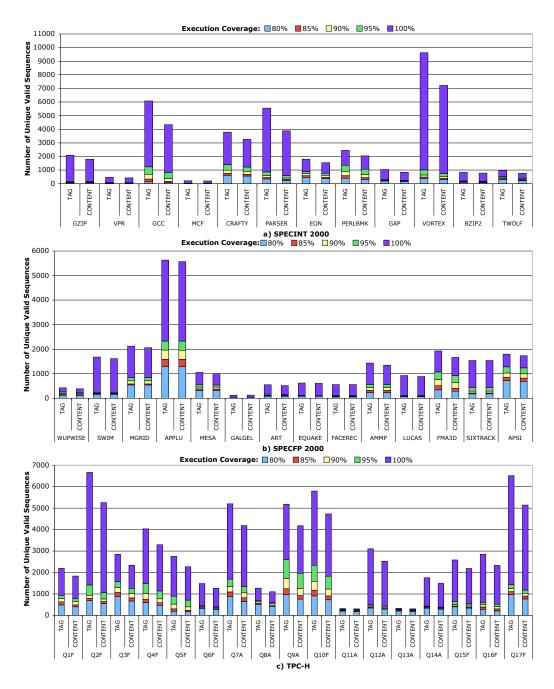

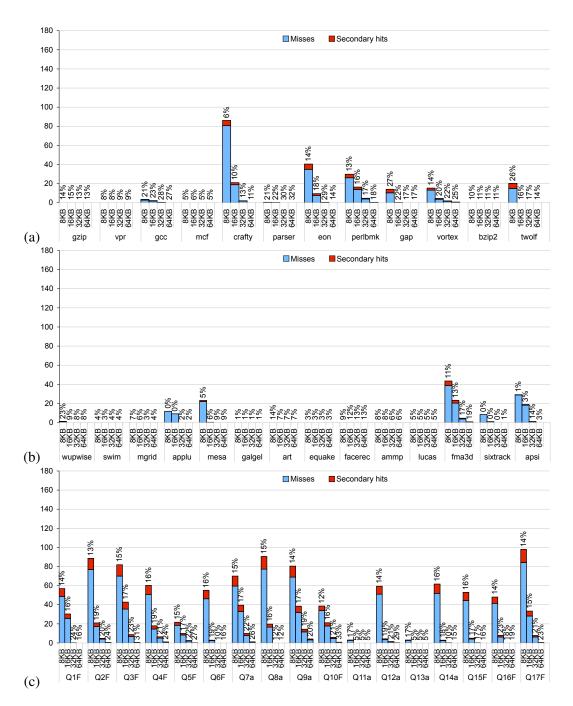

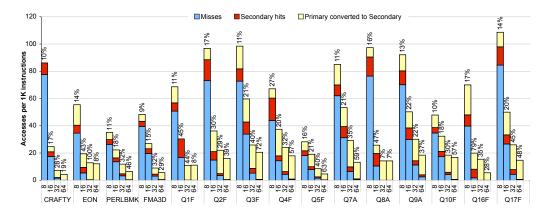

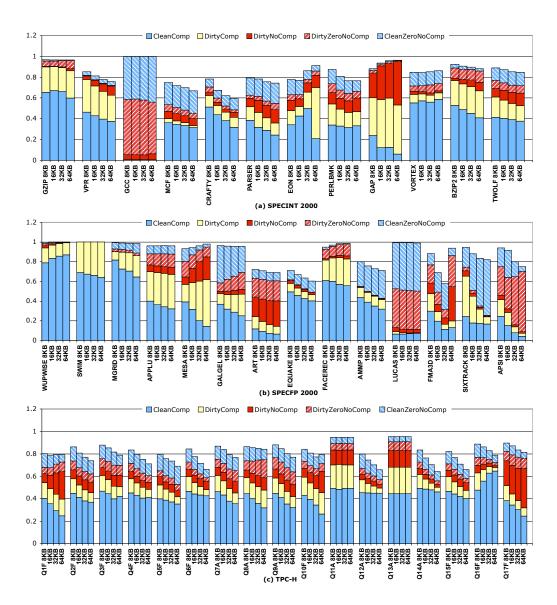

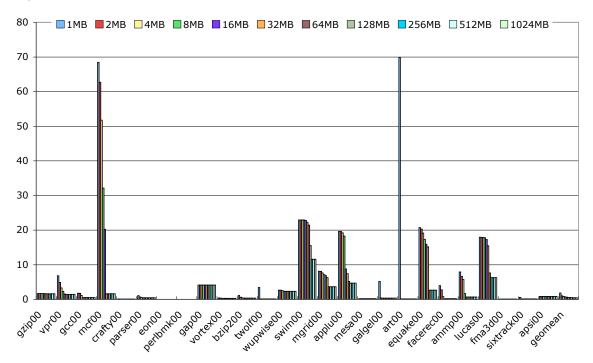

| 8  | Accesses per 1K instructions. CCD for an 8-way, 8 inst. per block, instruction     |    |

|    | cache, for entire blocks a) SPECINT 2000, b) SPECFP 2000, c) TPC-H                 | 42 |

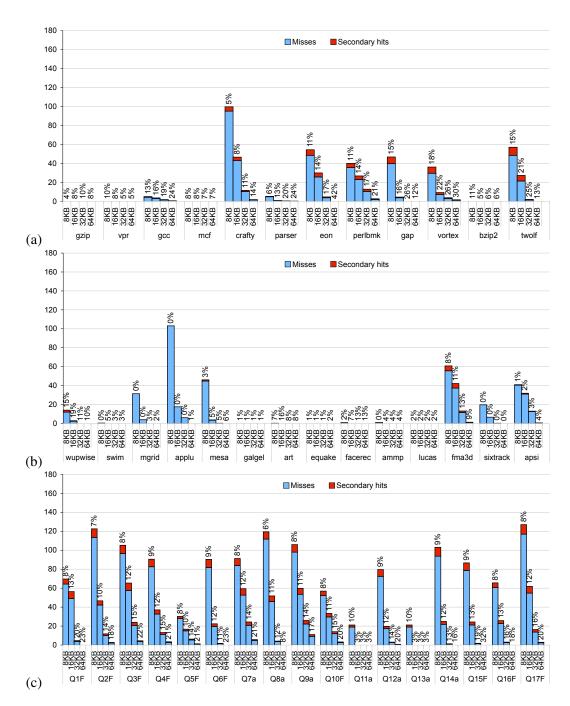

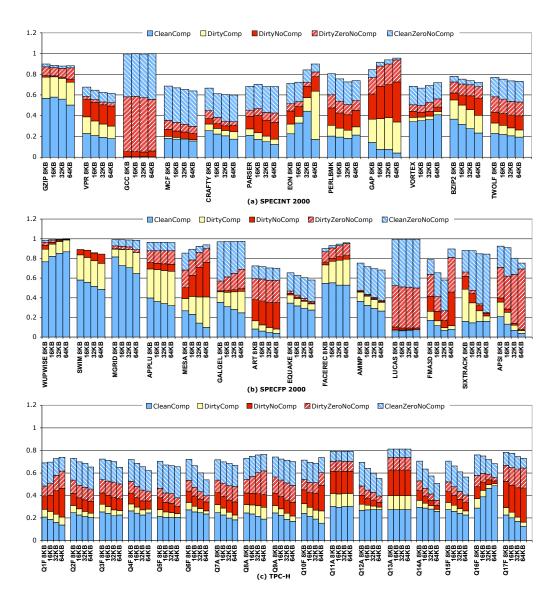

| 9  | Accesses per 1K instructions. CCD for an 8-way, 8 inst. per block, instruction     |    |

|    | cache, for valid blocks a) SPECINT 2000, b) SPECFP 2000, c) TPC-H                  | 43 |

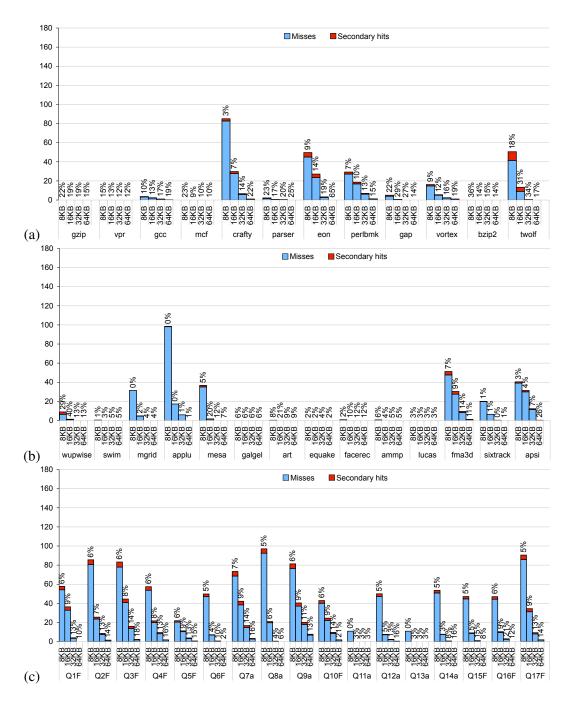

| 10 | Accesses per 1K instructions. CCD for an 8-way, 4 inst. per block, basic block     |    |

|    | cache, a) SPECINT 2000, b) SPECFP 2000, c) TPC-H                                   | 45 |

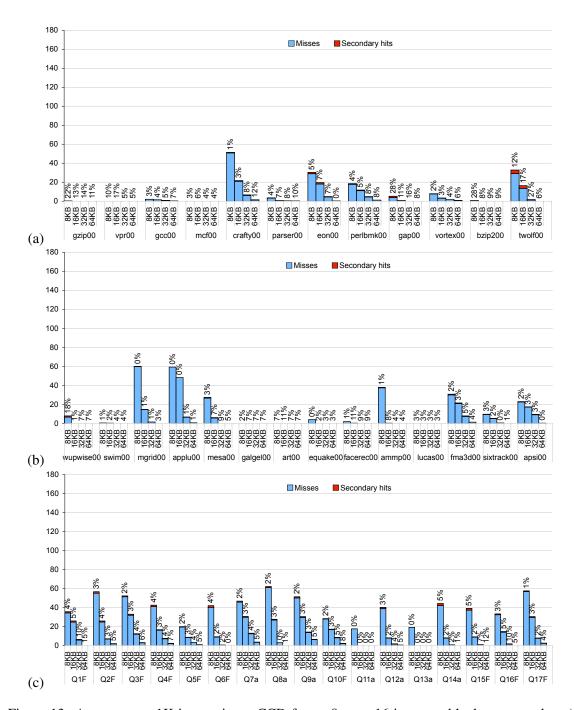

| 11 | Accesses per 1K instructions. CCD for an 8-way, 8 inst. per block, basic block     |    |

|    | cache, a) SPECINT 2000, b) SPECFP 2000, c) TPC-H                                   | 46 |

| 12 | Accesses per 1K instructions. CCD for an 8-way, 8 inst. per block, trace cache, a) |    |

|    | SPECINT 2000, b) SPECFP 2000, c) TPC-H                                             | 48 |

| 13 | Accesses per 1K instructions. CCD for an 8-way, 16 inst. per block, trace cache,   |    |

|    | a) SPECINT 2000, b) SPECFP 2000, c) TPC-H                                          | 49 |

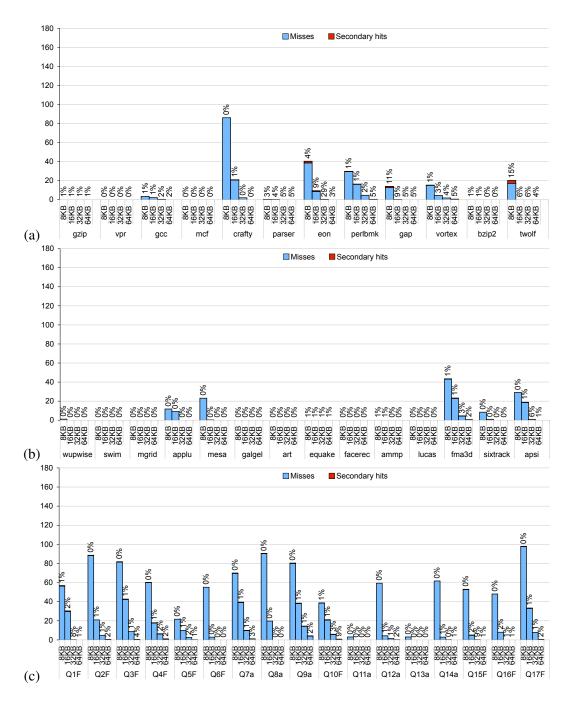

| 14 | Misses and Secondary hits per 1K instructions breakdown and CCD rates for a  |    |

|----|------------------------------------------------------------------------------|----|

|    | UCC 8-way, 8 instructions per block, instruction cache, for valid blocks     |    |

|    | 52                                                                           |    |

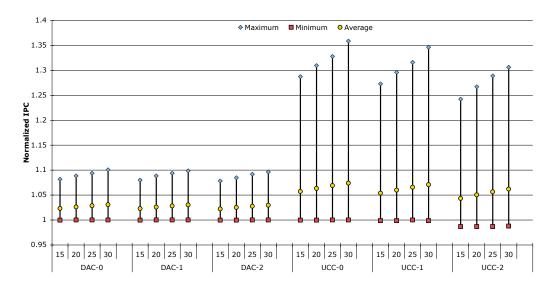

| 15 | Maximum, minimum and average of the normalized IPC performance of all bench- |    |

|    | marks for DAC and UCC for valid blocks. Results are shown for 15, 20, 25 and |    |

|    | 30 cycles L2 latencies and 0, 1 and 2 cycles secondary hit latencies         | 53 |

| 16 | The CATCH flow for a Cache miss, DR miss and HDD hit                         | 56 |

| 17 | The CATCH flow for a Cache miss, DR hit, Cache hit                           | 57 |

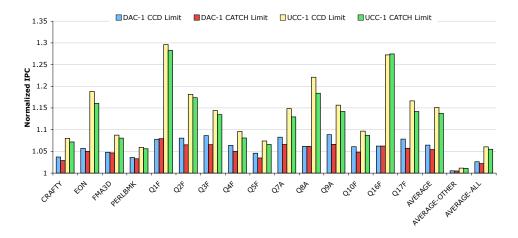

| 18 | Performance potential captured by oracle detection (limit) and CATCH for DAC |    |

|    | and UCC (16KB instruction cache, 20 cycles L2 cache latency)                 | 67 |

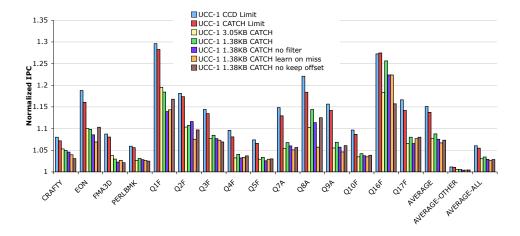

| 19 | Effects of applying different policies on CATCH performance                  | 69 |

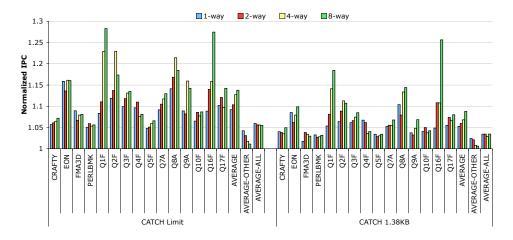

| 20 | CATCH with various cache associativities                                     | 70 |

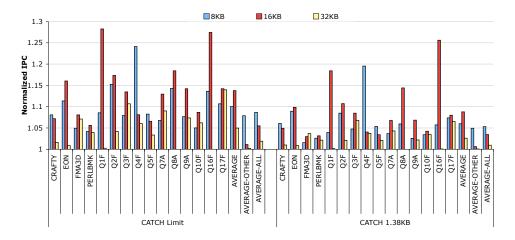

| 21 | CATCH with various cache sizes                                               | 71 |

| 22 | CATCH and 8 entry Victim Cache                                               | 72 |

| 23 | CATCH with next-line prefetching                                             | 73 |

| 24 | CATCH compared to an 18KB cache                                              | 73 |

| 25 | Normalized Energy Delay product when using a 1.38KB CATCH                    | 76 |

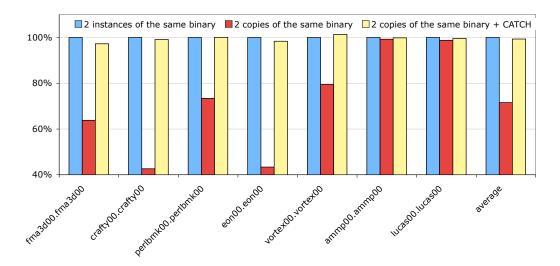

| 26 | Intrinsic and Extrinsic Text Cloning on Intel Pentium 4                      | 83 |

| 27 | Intrinsic and Extrinsic Text Cloning on Intel i7                             | 84 |

| 28 | Extrinsic Text Cloning overhead on Intel i7                                  | 84 |

| 29 | gLite job submission chain                                                   |    |

|    | (http://web.infn.it/gLiteWMS/index.php/techdoc/howtosandguides)              | 87 |

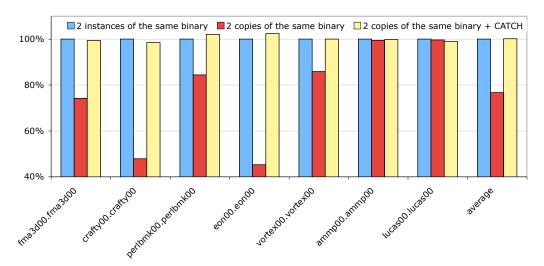

| 30 | Weighted SpeedUp. Detecting and eliminating ETC with overlapping program     |    |

|    | phases                                                                       | 91 |

| 31 | Weighted SpeedUp. Detecting and eliminating ETC with 500 million instructions     |

|----|-----------------------------------------------------------------------------------|

|    | shift in program phase                                                            |

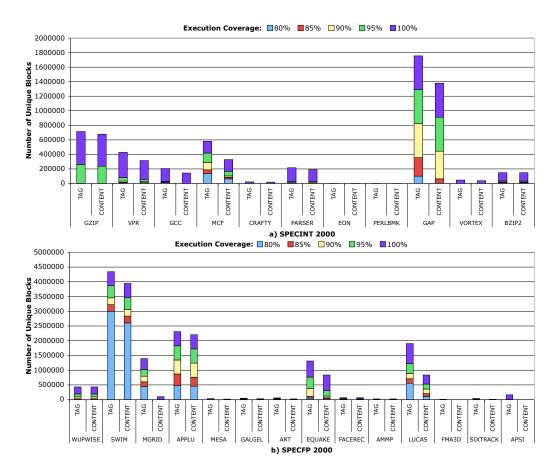

| 32 | Execution coverage of unique blocks for the a) SPECINT 2000 and b) SPECFP         |

|    | 2000                                                                              |

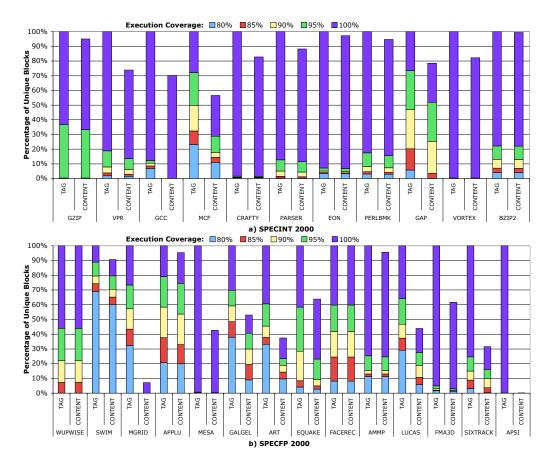

| 33 | Execution coverage breakdown of unique blocks in percentages for the a) SPECINT   |

|    | 2000 and b) SPECFP 2000                                                           |

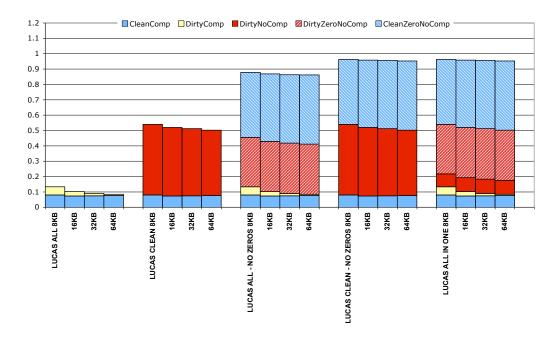

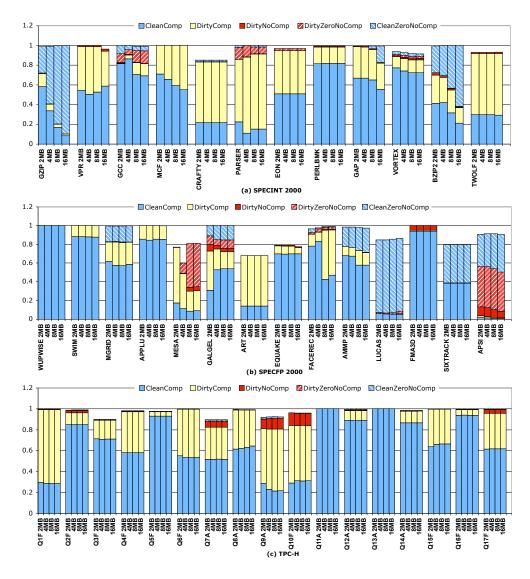

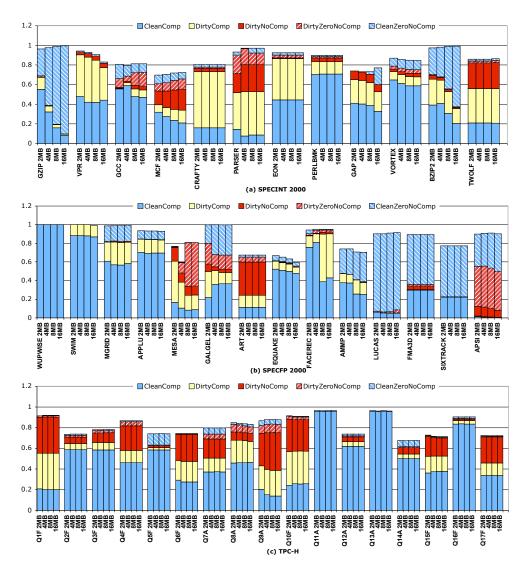

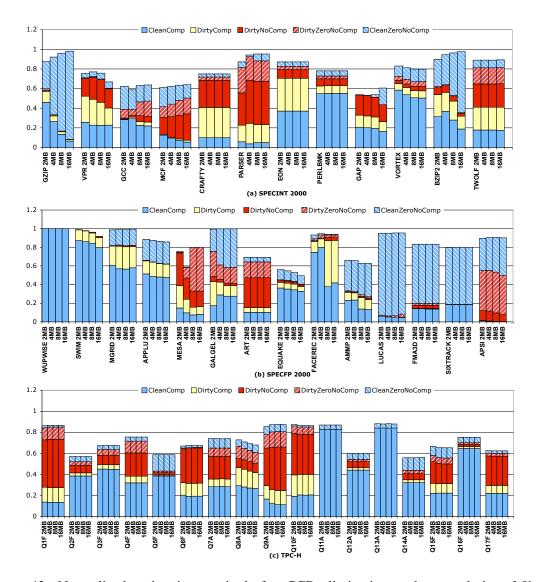

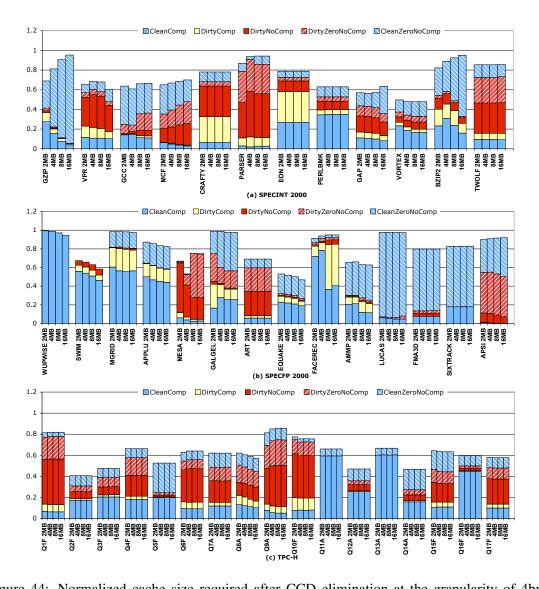

| 34 | Normalized cache size required after CCD elimination at the granularity of 64byte |

|    | blocks for benchmark LUCAS                                                        |

| 35 | Normalized cache size required after CCD elimination at the granularity of 64byte |

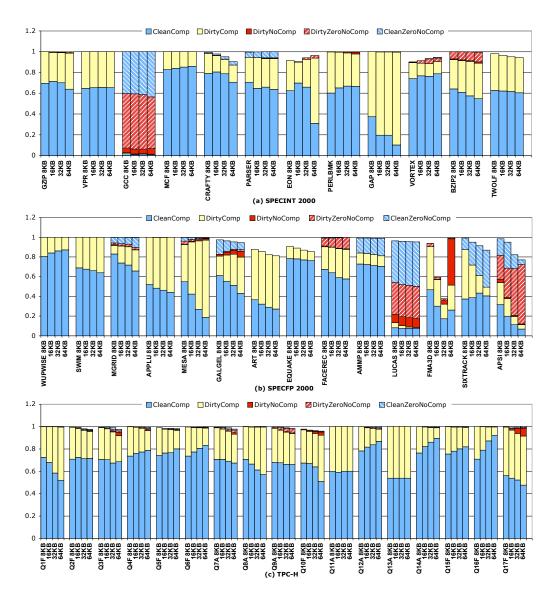

|    | blocks, a) SPECINT 2000, b) SPECFP 2000, c) TPC-H)                                |

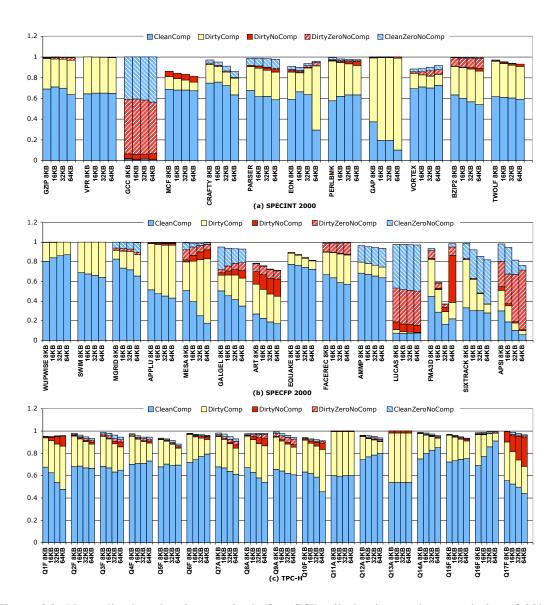

| 36 | Normalized cache size required after CCD elimination at the granularity of 32byte |

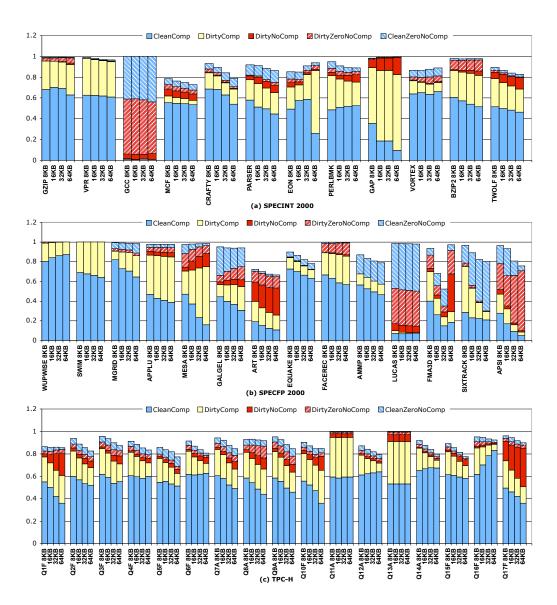

|    | segments, a) SPECINT 2000, b) SPECFP 2000, c) TPC-H)                              |

| 37 | Normalized cache size required after CCD elimination at the granularity of 16byte |

|    | segments, a) SPECINT 2000, b) SPECFP 2000, c) TPC-H)                              |

| 38 | Normalized cache size required after CCD elimination at the granularity of 8byte  |

|    | segments, a) SPECINT 2000, b) SPECFP 2000, c) TPC-H)                              |

| 39 | Normalized cache size required after CCD elimination at the granularity of 4byte  |

|    | segments, a) SPECINT 2000, b) SPECFP 2000, c) TPC-H)                              |

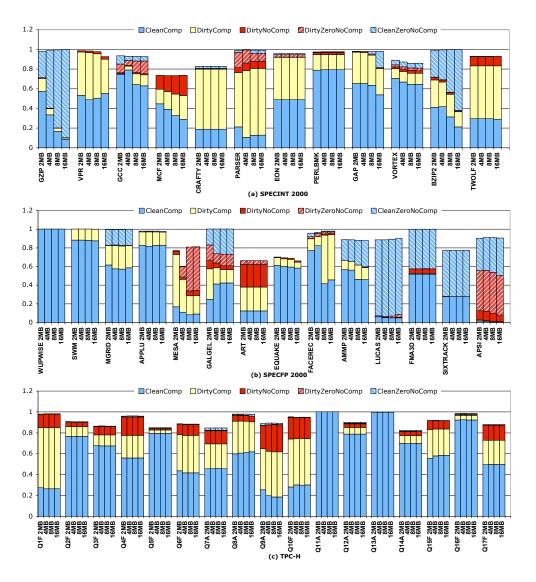

| 40 | Normalized cache size required after CCD elimination at the granularity of 64byte |

|    | blocks, a) SPECINT 2000, b) SPECFP 2000, c) TPC-H)                                |

| 41 | Normalized cache size required after CCD elimination at the granularity of 32byte |

|    | segments, a) SPECINT 2000, b) SPECFP 2000, c) TPC-H)                              |

| 42 | Normalized cache size required after CCD elimination at the granularity of 16byte |

|    | segments, a) SPECINT 2000, b) SPECFP 2000, c) TPC-H)                              |

| 43 | Normalized cache size required after CCD elimination at the granularity of 8byte  |

|----|-----------------------------------------------------------------------------------|

|    | segments, a) SPECINT 2000, b) SPECFP 2000, c) TPC-H)                              |

| 44 | Normalized cache size required after CCD elimination at the granularity of 4byte  |

|    | segments, a) SPECINT 2000, b) SPECFP 2000, c) TPC-H)                              |

| 45 | Performance improvement of an out-of-order processor with perfect cache (Same     |

|    | as Figure 2)                                                                      |

| 46 | Misses Per 1K instructions for various LLC cache sizes)                           |

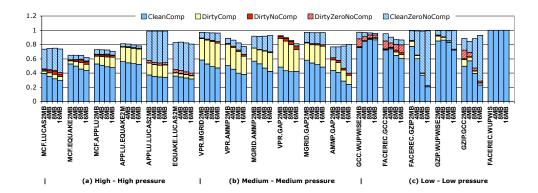

| 47 | Normalized cache size required after CCD elimination at the granularity of 16byte |

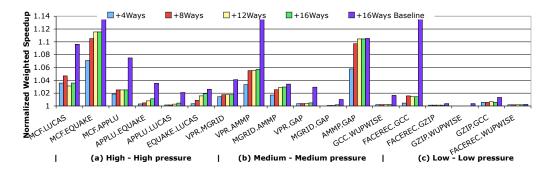

|    | segments for a) High - High, b) Medium - Medium and c) Low - Low pressure         |

|    | benchmark combinations                                                            |

| 48 | Normalized cache size required after CCD elimination at the granularity of 16byte |

|    | segments for a) High - Medium, b) High - Low and c) Medium - Low pressure         |

|    | benchmark combinations                                                            |

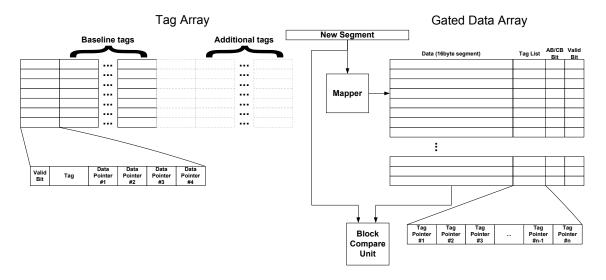

| 49 | The functional componets of the proposed Content Duplication Aware Cache 120      |

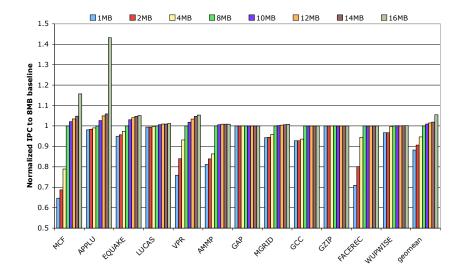

| 50 | Normalized IPC speedup on the 8MB baseline for various cache sizes                |

| 51 | Normalized IPC speedup on the 8MB baseline when increasing tag array 123          |

| 52 | Normalized IPC speedup on the 8MB baseline when decreasing data array 125         |

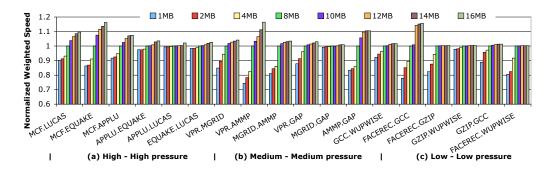

| 53 | Normalized IPC speedup on the 8MB baseline for various cache sizes for a) High    |

|    | - High, b) Medium - Medium and c) Low - Low pressure benchmark combinations 126   |

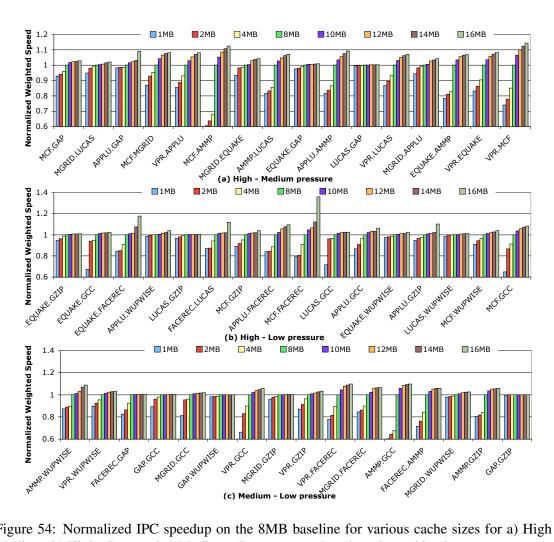

| 54 | Normalized IPC speedup on the 8MB baseline for various cache sizes for a) High    |

|    | - Medium, b) High - Low and c) Medium - Low pressure benchmark combinations 126   |

| 55 | Normalized IPC speedup on the 8MB baseline when increasing tag array for a)       |

|    | High - High, b) Medium - Medium and c) Low - Low pressure benchmark combi-        |

|    | nations                                                                           |

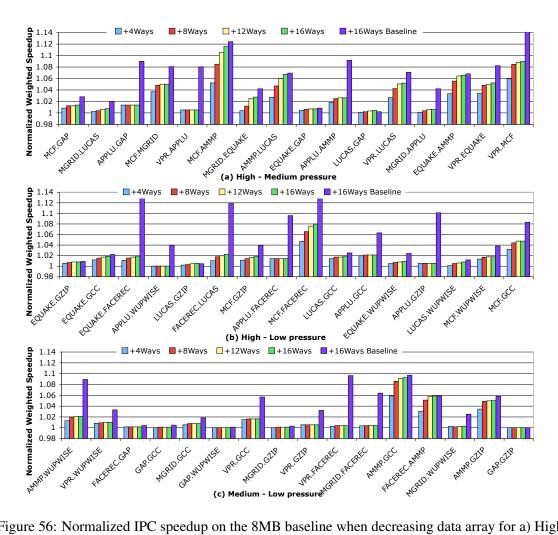

| 56 | Normalized IPC speedup on the 8MB baseline when decreasing data array for       |

|----|---------------------------------------------------------------------------------|

|    | a) High - Medium, b) High - Low and d) Medium - Low pressure benchmark          |

|    | combinations                                                                    |

| 57 | Normalized IPC speedup on the 8MB baseline when decreasing data array for       |

|    | a) High - High, b) Medium - Medium and c) Low - Low pressure benchmark          |

|    | combinations                                                                    |

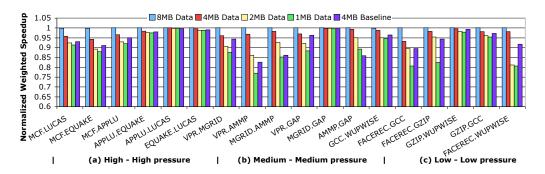

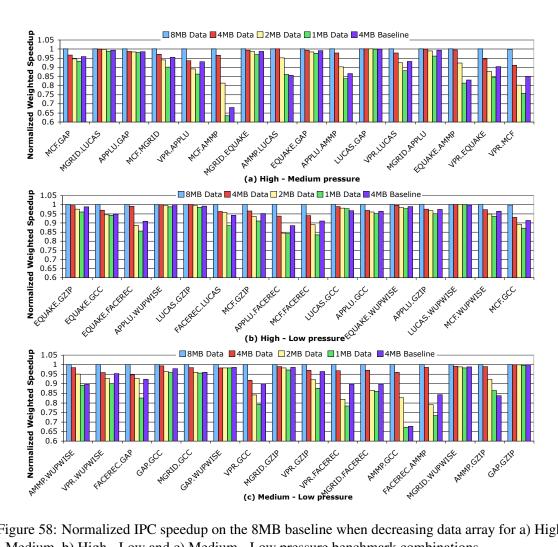

| 58 | Normalized IPC speedup on the 8MB baseline when decreasing data array for       |

|    | a) High - Medium, b) High - Low and c) Medium - Low pressure benchmark          |

|    | combinations                                                                    |

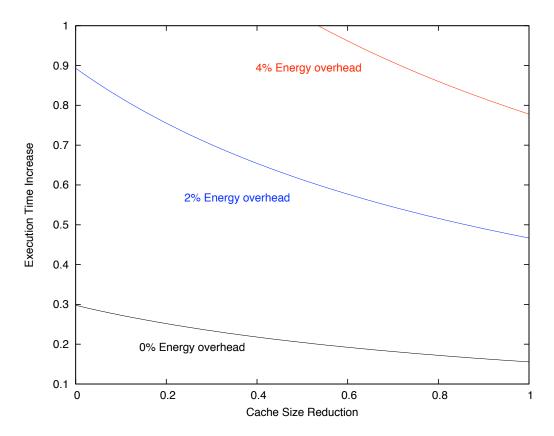

| 59 | Energy profiling of increasing execution time and decreasing LLC data array 131 |

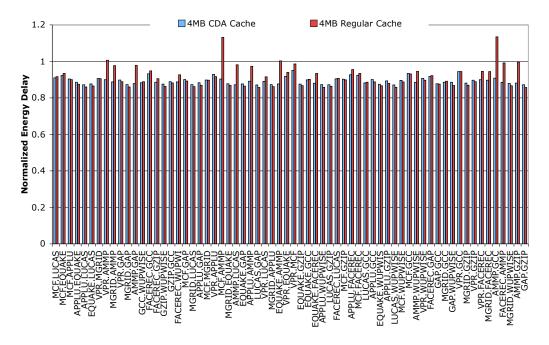

| 60 | Normalized Energy delay for a 4MB CDA cache (with double the number of tags)    |

|    | and a 4MB regular cache                                                         |

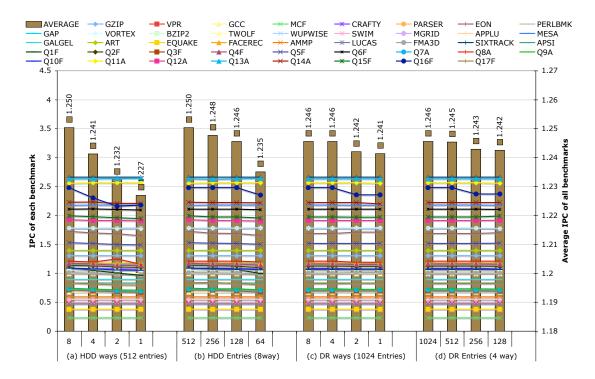

| 61 | Performance potential of CATCH for a UCC using various sizes and associativity  |

|    | of HDD and DR for 16KB cache for valid blocks                                   |

# **Chapter 1**

### Introduction

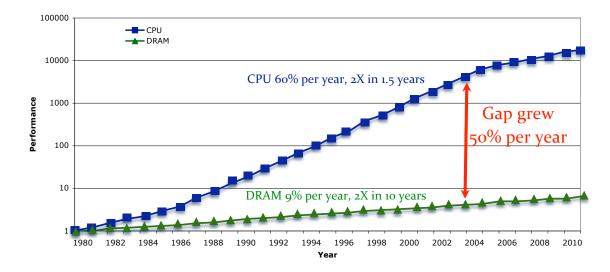

The importance of caches and memory hierarchy has increased over time due to the growing gap between processor and memory performance [2]. The memory gap, as shown in Figure 1, has been growing by more than 50% in the last decade and has become more pronounced the last few years with the wider use of Simultaneous Multithreading (SMT) and Chip Multiprocessor (CMP). The applications are also becoming more demanding by exploiting all the computational power provided by the state of the art processors.

The combination of multi-cores and multi-threading is effective in improving processor utilization as long as the memory hierarchy can satisfy all running threads instructions and data needs. Consequently, modern processors devote a large fraction of their real estate for the cache hierarchy and numerous research studies are conducted on how to efficiently share the cache hierarchy among concurrent on-chip threads [3, 4, 5]. These proposals are aimed to overcome various daunting memory related challenges.

Figure 1: Memory Gap [1]

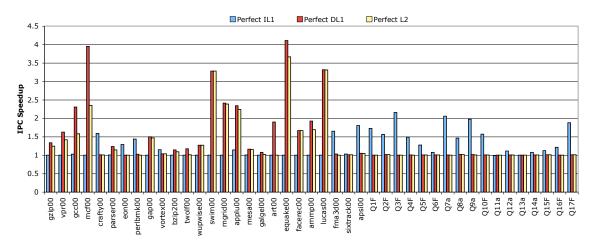

Figure 2: Performance improvement of an out-of-order processor with perfect cache

### 1.1 Memory Challenges

The performance of caches has always been limited by their size and energy constrains. In order for the caches to be beneficial they have to be small, because this will provide lower latencies, but also need to be energy efficient since they occupy a large portion of the chip.

Adding more levels in the memory hierarchy and bigger caches in the processors is not the answer anymore since both approaches are costly. The Figure 2 shows the performance potential of a high performance processor using various workloads with a perfect L1 instruction, L1 data

and L2 unified cache. The results indicate that there still room to improve the memory gap. We can also observe that different application types to need more instruction cache and others more data and L2 cache. The main challenges of caches are the following:

- Average Latency: The ultimate goal is to reduce the average latency as low as possible while maintaining the same or similar cache size. This can be achieved by several mechanisms, like prefetching, victim caches, e.t.c [6, 7]. Reducing misses, by using prefetching for example, helps reduce the average access latency of the cache.

- Effective Capacity: Another challenge is to increase the effective capacity of a cache without increasing the physical area. The most common technique to achieve this is by compressing the data in the cache. In this way, more data will fit in the same cache size. A trade off when using compression is to increase the hit latency for larger capacity. The goal though is to achieve a total lower average latency, so the increase in the hit latency will be eventually compensated by the savings due the cache miss reduction.

- Bandwidth Requirements: With the use of SMT and CMP processors, requests to the main

memory and lower levels of the cache have increased putting pressure to limited off-chip

bandwidth. To overcome this challenge several techniques have been proposed, including

the use of compressed data through the bus.

- Power Constraints: The power constraints have been and will remain to be a primary

design constraint for the years to come. The challenge aimed to provide high performing

memory hierarchies and low energy has been the subject of several research projects and is

still an open issue.

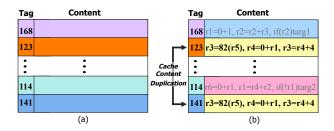

Figure 3: Cache Content Duplication (a) Without CCD, (b) With CCD

#### 1.2 Thesis Contributions

This thesis identifies a new cache property that may influence cache performance: the Cache-Content-Duplication (CCD). This phenomenon occurs when there is a miss for a block in a cache and the content of the missed block resides already in the cache in another block with a different tag. Therefore, CCD is a manifestation of redundancy in the cache content. For example, Fig. 3.a shows an instruction cache where each block is identified by its tag and Fig. 3.b shows an instruction cache which is aware of the block content. This example shows that two different blocks, with tags 123 and 141, have identical content. If block 141 is evicted and later we have a miss on it, the content of 123 can be used without accessing a lower level of the memory hierarchy.

By identifying and exploiting CCD we can address most of the memory challenges mentioned earlier. Removing CCD from caches helps increase the effective cache capacity and therefore improve the cache performance. Also, by identifying CCD and reducing the cache misses will affect the bandwidth since the requests for data reduced. Compressing the data array and power gating its inactive portion can reduce static leakage of the cache.

The main contributions of this thesis are the following:

• CCD for Instruction Caches: In Chapter 4 we investigate the potential of CCD in instruction caches. We will characterize the phenomenon of CCD and measure its frequency in various types of instruction caches like block-based caches, trace caches, and normal caches.

We will also discuss which cache parameters might influence CCD and what optimizations can be applied to improve the detection of CCD in caches.

Then we propose two new cache types, the Duplicate-Aware-Cache (DAC) and the Unique-Content-Cache (UCC) that can exploit the CCD phenomenon. Both caches aim to reduce the cache latency on a miss by using a duplicated block in the cache while the UCC cache also increases the effective cache size by allowing unique blocks to enter the cache.

Furthermore we propose CATCH, a hardware mechanism that can dynamically detect CCD, and an investigation of its performance for DAC and UCC instruction caches. The various components of the mechanism are described, and various optimizations are proposed to increase performance and to reduce the cost of the mechanism.

In Chapter 5 we study another case of CCD for instruction caches, the **Extrinsic and Intrinsic Text Cloning**. Text Cloning refers to the phenomenon where identical code, from the same or different applications, coexist simultaneously in an instruction cache. We investigate the effects of Text Cloning on real platforms to quantify the performance degradation due to this type of redundancy. Finally, we discuss possible applications of CATCH mechanism to detect and eliminate this text cloning.

- CCD for Data Caches: Chapter 6 investigates the potential of CCD for data caches. We

present analysis of duplication in data caches at the block level and discuss why CCD optimizations are hard to apply on data caches.

- CCD for Last Level Caches: In Chapter 7 we present a study on Last Level Caches both for single and multiprogram workloads. Specifically we measure the frequency of CCD in a LLC cache at various granularities. We also propose a new cache design, the Content Duplication Aware (CDA) cache uses extra tags to insert more compressed data in the data

array or improves energy efficiency by switching off part of the data array that is not used due to compression.

An optimistic implementation of CDA is evaluated in terms of performance and energy to establish the potential of the proposed approach.

#### 1.3 Main Output of this Thesis

The work during this thesis resulted in the publication of a journal paper, a conference paper, a workshop paper (later published in a special issue journal), three technical reports and two posters.

A technical report [8] described CCD in instructions caches and provided an initial analysis of the phenomenon. An abstract and a poster of this technical report was presented in ACACES 2005 [9].

The effects of detecting duplication at the granularity of valid blocks were presented in ACACES 2006 [10] as a poster. Next there was another technical report [11] that extended the first with performance analysis and provided a detail mechanism to dynamically detect and exploit CCD, CATCH. The same work was later published in DATE [12].

A special case of CCD, the Text Cloning, was presented during WIOSCA 2010 workshop [13]. The paper was later published in LNCS journal. Also, an extension of the DATE paper with more thorough analysis of the effects of CCD and CATCH on other caches optimizations, like prefetching, was accepted for publication in TACO journal in 2011 [14]

Finally, a framework to identify the simulation regions for benchmarks was developed during this thesis and appears as a technical report in [15].

#### 1.4 Other Output from this Work

During this thesis we have also worked on other projects that resulted to publications and a patent.

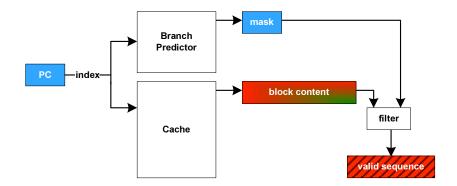

#### 1.4.1 Improving Branch Prediction by Considering Affectors and Affectees Correlations

Branch prediction has been the subject of several papers. In this work [16, 17] we have investigated the potential of direction-correlations, for both affectors and affectees, to improve branch prediction. The correlations are determined based on data-flow graph information and used to select a subset of history bits that affect a prediction.

The main contribution of this work is the insights that provide on how and why predictors work using history and the possibility of predictors that can efficiently learn correlations that may be non-consecutive from long branch history.

#### 1.4.2 Entry Replacement Within a Data Store

A mechanism to improve the performance of value predictors was developed in [18, 19]. A value predictor's performance relies on the predictability of the program phase. Some program phases are very predictable, for example streaming or stride behavior, while others are completely random. The more load instructions we can keep history of in the value predictor the better performance we will have.

Investigating the behavior of several applications we observed that only a fraction of the load instructions is really predictable and the rest just pollutes the value predictor and evicts useful information.

A replacement predictor was proposed that predicts the predictability of a bigger subset of load instructions by approximating a large direct mapped value predictor without tag matching and

using hashed information. Using this table we effectively profile the behavior of an application, or a certain phase of it, and decide whether the value predictor should be updated or not with a certain load instruction.

The main contribution of this work was a novel replacement policy to select the best values to update a value predictor using a small direct mapped table.

## 1.5 Thesis Outline

The rest of the thesis is organized as follows: In Chapter 2, a background on memory optimizations and previous work related to cache redundancy is discussed. The Chapter 3 presents the metrics, the simulation environment and the benchmarks that were used in this thesis. In Chapter 4, we discuss our work on Instruction Caches and Chapter 5 presents another case of CCD for instruction. Chapter 6 investigates the potential of CCD in Data Caches. In Chapter 7, an analysis of CCD in LLCs is presented and a mechanism is proposed to exploit CCD. Finally, Chapter 8 provides conclusions and directions for future work.

# **Chapter 2**

## **Background and Related Work**

Since their introduction to the motherboards as fast small off-chip memories and later their integration into the processors as on-chip memories, the caches have improved the processor's performance. This Chapter will provide a background on several memory optimizations that have been proposed with more emphasis on previous work related to cache compression optimizations.

### 2.1 Memory Hierarchy Optimizations

The caches have been the central to numerous research studies, all aiming to cover this gap more efficiently. Several techniques have been proposed to improve various aspects of caches by reducing their miss rates, size, latency, and energy. Most of these techniques attempt to exploit different types of properties of memory addresses and data, such as locality [20], predictability [21, 22], and redundancy [23, 24].

The rest of this section categorizes and describes the most important techniques that are applied to improve cache performance and comments on different approaches.

#### 2.1.1 Replacement Policies

The optimal cache replacement policy has been the holy grail in cache optimizations research. The decision for which block to replace from the cache is very critical. The policy has to choose a block that hasn't been used for a long time but also to predict, in a way, that will not be reused in the near future.

Replacement policy's performance always depends on the workloads characteristics so a good replacement policy must be able to adapt to different phases of a program. There are mainly three different approaches that researchers are using to develop or improve a cache replacement policy.

The first approach is the *Optimal Replacement Approximation* [25, 26]. The main goal is to predict which block in the set will be needed further in the future. This can be achieved by keeping a history of the previous replacements and accesses and employing a predictor to indicate the victim. The new block to be inserted in the cache can also be the victim and here the new block is just bypassed, and there are no replacements in the cache.

The second approach is the *Adaptive Replacement Policies* [27, 28, 29]. In this case, researchers attempt to categorize different program phases, such as streaming or good locality or big workloads, and dynamically identify these phases. Once the behavior of the application that is exhibited in the current phase is identified, the appropriate replacement policy can be applied. It is very common that a phase that exercises a big workload is best handled by an MRU policy, while a phase with a good locality will be exploited better using an LRU policy.

Finally, the third approach is the *Global Replacement Policies* [30, 31, 32]. The idea behind this approach is that some of the sets in the cache are very hot while some others are rarely used and can also have empty slots. Using a secondary index the Global Replacement Policies attempt to find an alternative place to insert a block if it doesn't fit in its primary location. Effectively the

Global Replacement Policy attempts to emulate a fully associative cache using a direct cache or a set associative cache. By doing this, we can achieve better utilization without bearing the high cost of accessing a fully associative cache.

#### 2.1.2 Prefetching

Another common optimization is the cache prefetching. The researchers noticed that since the memory hierarchy on a miss is not fast enough to cover the throughput of out-of-order processors then the missed block should be predicted and prefetched before the processor requests it.

To achieve prefetching, future knowledge is required to predict the next access. Since this not possible, even with profiling it cannot be 100% accurate, many have tried to exploit the program regularities to predict the next missed block and prefetch it. We divide the previous work on cache prefetching into three categories.

The first category is the *Compiler assisted prefetching* [33]. The ideal prefetcher will be the one that knows the future and the best way to learn the future is to take a look by profiling. Using profiling and programmer's knowledge the compiler can be armed with the ability to "know" the future and add special instructions that will initiate prefetching when necessary. This approach is very fast and accurate since we have almost perfect knowledge of the program behavior and there is no need for probing and updating predictors. The downside of this technique is that it requires profiling which is extra work and not always possible, for example with legacy code. Also, different program inputs may lead to multiple control flow paths and this will require either more profiling or less accurate prefetching.

Another category of prefetching is the *Fetch streaming* [34, 35]. The use of history predictor is very common in processor designs and has been also used for prefetching. Although sometimes a simple next line predictor can be very efficient most of the times the addresses of the instructions

executing are not continuous. The authors in this category tried to create a chain of dynamic instructions that do not have to be continuous in the static code to use this later for prefetching. Once the sequence of instructions is identified and stored in the predictor the first instruction of the sequence is assigned as the trigger instruction. When the program execution reaches the trigger instruction, a sequence of events is also initiated by the predictor to execute the instructions that were also executed in the past when the trigger was called. This will result to speculative data and instructions to prefetched in the cache.

The last category is the *Runahead Execution* [36, 6, 37] where mechanisms are proposed to speculative run the application and force the misses before they are requested so they will prefetched in cache. By exploiting the extra throughput provided by the SMTs when at least one thread slot is idle, the processor can run a speculative version of the application in parallel with the normal execution but slightly forward few hundred of instructions. If the speculation is correct, useful data will be fetch in both data and instruction caches. A very important detail of the runahead execution is to detect the optimal distance between the runahead version of the application and the normal version. Going too much forward means that unnecessary information will be fetched that may pollute the cache and cause more misses, while going too little forward means that the runahead execution will not be fast enough to fetch the requested information on time.

## 2.1.3 Compression

Data compression techniques have been around for a long time. People noticed from the beginning of writing that some words are most common than others and if we represent those words with fewer letters then the size of the text gets smaller. The same idea applies when we compress bits and bytes in a computer's memory and using a dictionary we represent the most

common sequences of data that can be from few bits to a whole memory page, with smaller codes aiming to reduce the space needed to store our data.

The data compression was first applied in disks in the early 1990s where the size of a hard disk was at the range of few megabytes to few tens of megabytes. There were several DOS [38] applications to compress files and directories in the disks to increase the free space. Today, disk compression is still used but is mainly applied to increase the effective bandwidth in networks such as the internet or any other network systems. Venti [39] is an example where disk compression is used to save space in a network storage system intended for archival data. Venti hashes the data to detect and eliminated duplicated information stored in magnetic disks. Also, a common application of disk compression is for files that are going to be distributed through the internet or any other local network to save bandwidth.

Another emerging application of compression is in the region of virtualization. Virtual caches might have vast amount duplication because they might be even running the exact image of a system multiple times. This duplication can be eliminated by using mechanisms [40] to detect whole memory pages that contain the same data and merge them. A similar approach is used by the Linux operating system and is called Kernel SamePage Merging (KSM) [41, 42] where a hypervisor is checking all memory pages and merge any duplicated pages, pages that contain the exact same data. In case of a write on such a page the dirty page is copied (copy-on-write). KSM idea was first proposed for virtual memory and then applied to Linux operating system for the first time on version 2.6.32.

Finally, another application of Compression is the cache compression, which is also the most relevant to our work. More specifically in caches the compression is very important to keep them small and fast. By compressing the data we increase the effective cache size without increasing

its physical size that will lead to longer access times and higher energy per access. Also by transferring data in a compressed form between various levels in the memory hierarchy the effective memory bandwidth is also increased.

There are two different approaches in cache compression, the *Dynamic Compression*[43, 23,

44, 45, 46, 47, 48, 49, 50, 51, 23, 52, 53, 54] and the *Static Compression* [55, 56, 57, 24, 58, 59].

Dynamic Compression provides flexibility and adaptivity to the program phase changes. Several researchers adopted this approach and either by building a dictionary through profiling or by dynamically detecting the redundancy they tried to improve the cache performance by increasing

the effective cache size. Furthermore, the dynamic compression also provides the option to turn

off compression if the overheads become too high on a certain program phase.

On the other hand the *Static Compression* gives more room for transformations and a global view of the application in order reduce the required space even more. The main disadvantages of Static Compression are that it cannot be applied to legacy code either can be turned off during execution.

A more extended discussion on Cache Compression techniques is presented in Section 2.

#### 2.2 Related Work on Compression

This thesis will focus on the redundancy of the memory and cache content, which has also been the subject of several previous works. The main objectives of memory hierarchy redundancy optimizations are to increase the effective memory/cache capacity or to achieve higher bandwidth during the information transfer between the different levels of the memory hierarchy or both. This will result to performance improvement and/or energy reduction.

Previous work on memory hierarchy compression can be separated in two main categories, the Dynamic Compression which means the redundancy is detected dynamically and compressed in any level of the memory hierarchy and the *Static Compression* where the data, either instructions, or information, are compressed before they are loaded in the memory.

#### 2.2.1 Dynamic Compression

A scheme for main memory on-line compression was first proposed by Douglis [43]. This work is targeting the main memory to reduce the I/O between the memory and the disk. Keeping the LRU memory pages compressed the main memory can accommodate more pages, and thus reducing the misses and the need for I/O. The LZRW1 dictionary based algorithm is used for the compression with a 16KB hash table.

Kjelso and Gooch [23] proposed a hardware implementation of the X-Match dictionary compression algorithm for main memory data. Their algorithm requires about 30% more hardware than previously proposed hardware designs but can achieve 2-3 times faster compression and decompression rates.

Lefurgy et al. [44] studied the concept of keeping compressed code in main memory and "software decompressing" on a cache miss. More specifically, frequently used instructions, in the original code, are replaced by pointers to an entry in a 64K instruction dictionary. The authors observed that the high overhead of software decompression was slowing down the benchmarks, and they show that selective compression can reduce this performance loss.

The high redundancy of a subset of values in data caches was identified in [45]. A Frequent Value Cache (FVC) was proposed to hold the frequent values in compressed form. The FVC is accessed in parallel with a Direct Mapped Cache (DMC) and in case of a cache miss and a hit on FVC the miss was served from there. The FVC is updated only on replacements from the DMC.

Very relevant to our work is [46] that introduces the notion of address correlation: two different addresses are correlated when at the same time they contain the same value. Address correlation

can improve performance if on a cache miss the correlated address is found in the cache in another location. The authors investigated the limits of oracle address correlation, and found it to be significant, but did not propose a mechanism for detecting it.

Molina et al. [47] noticed the value replication in the cache and proposed the use of a decoupled tag array and data array in order to keep unique values in the data array and pointers from the tags to these values. They called this type of a cache a Non Redundant Data Cache.

In the same concept of [47] the authors of [48] proposed the Content-Based Block Caching. The difference from the previous is that is done for a buffer cache and given the advantage of higher latencies in software and memory availability the authors achieve to eliminate most of the limitations that [47] faced on hardware.

Alameldeen and Wood [49] keep information compressed, for both instructions and data, only in L2 cache and can dynamically choose to keep data in uncompressed form when the overhead of compression may cause degradation in performance.

Hallnor and Reinhardt [50] proposed a scheme that can map multiple compressed blocks into a single physical cache block using an Indirect Index Cache. A compressed block will require fewer segments for its data leaving additional storage for other blocks. This scheme maintains compressed data both in main memory and on-chip and enables the data to travel through the bus in compressed form. Therefore, this approach offers both extra space on main memory and cache, and a higher transfer rate from main memory to cache.

Biswas et al. [51] investigate the phenomenon of data similarity in multi-execution programs. They observed that when multiple instances of the same application are running on a multicore sharing the same L2 cache, their data are usually very similar.

Many researchers have also noticed that there is a big tradeoff of compressing only zeros instead of all possible values. The main idea is that the zero runs in the data are very common and although may not cover a big part of the execution they are much simpler to compress.

Kjelso and Gooch [23] proposed an extension to their hardware implementation X-Match just to zero runs and they called it X-RL.

The zero values were exploited by Villa et al. [52] to save energy. They propose to use an extra bit for every byte stored in the cache that indicates if the block is zero or not. In case of a zero block only that one bit is needed to be read.

Ekman and Stenstrom [53] detected cache blocks that are for zeros using 1 extra bit per block in the Block Size Table (BST). The BST has as many entries as the TLB array and each entry in the BST has pageSize/blockSize bits. In this way, once a zero block arrives in the L2, it's marked it in its corresponding BST entry and they don't cache it at all. Eventually, if that block is referenced again the BST will indicate that the block is all zeros.

The benefit of eliminating zero blocks was also studied by Dusser et al. [54]. The authors propose an extra cache, called Zero-Content cache, to keep track of zeros in the regular cache. Each entry in the ZC cache contains a tag (the sector address) and a number of N bits. N equals to SectorSize/CacheBlockSize and each bit corresponds to one of these blocks. A cache miss followed by a ZC cache hit means that the block is all zeros and an access to lower levels of memory hierarchy is saved.

Finally, the effects of compression to the area and energy were studied by Kim et al. [60]. They proposed the use of two smaller caches, instead of a big one, and smaller block size. All the compressible blocks reside in the first cache while the uncompressed blocks can be in both caches. The authors show that using their scheme can save both and energy and area as compared to a conventional L2 cache with at most 0.5% performance degradation.

#### 2.2.2 Static Compression

Lefurgy et al. [55] explored the idea of keeping compressed code in instruction memories of embedded processors. Based on static analysis, common sequences of instructions are assigned unique codes. These codes are stored in instruction memory and are expanded to their original form when requested for execution.

Benini et al. [56] proposed a dictionary based compression technique for firmware code executed on embedded systems. The aim for this work was to reduce the energy required during execution by compressing the most commonly used instructions to reduce memory accesses. This scheme does not require any processor modification since the instruction decompression is performed on the fly by a hardware module between the memory and processor.

Hines et al. [57] proposed the use of an Instruction Register File (IRF) for holding frequently executed instructions. An integrated compiler/hardware mechanism exploits this to reduce the code size and power requirements and to improve performance.

#### 2.3 Code Compaction

Code compaction methods [24, 58, 59] are used to reduce the executable code size without a need to decompress the compacted code for execution. Code compaction work could be easily labeled as *Static Compression* and included in the previous Section, 2.2.2, but we wanted to differentiate it because it deals only with instructions and employs very special optimizations.

The main idea behind most compaction techniques is to have the compiler back-end identify repeated sequences in a program and eliminate the repetition by either *cross-jumping* or *procedural abstraction*. Cross-jumping replaces all instances of a repeated sequence with a jump to a new location that contains a single copy of the repeated sequence. Procedural abstraction is used to

convert a repeated sequence to a procedure and replace the repeated sequences with calls to this procedure. Control flow dominance criteria are used to decide which of the two methods is applied in each case of repetition.

Code compaction transformations have also been proposed to convert "superficially" dissimilar sequences to repeated. For example, two sequences can perform exactly the same computation using different registers. These differences can be eliminated using move instructions to rename registers prior and after executing a compacted repeated sequence. The main cost of code compaction is run-time overhead due to the extra instructions executed to steer the control flow to/from unique copies of repeated sequences and to transform dissimilar sequences to similar. This overhead, however, can be offset by a possible reduction in instruction cache misses.

#### 2.4 Dynamic VS Static Techniques and Mechanisms

The benefit of static compression comes from the advantage that the compiler and the programmer can have a bigger picture of the application and that enables better transformations and optimizations to eliminate redundancy. On the other hand the Dynamic approach, although limited in the number of transformation, can be adaptive and applicable to legacy code. Especially the adaptivity seems to be a very important factor in cache optimizations since the behavior of an application can change so radically that a specify optimization will degrade, rather than improve, its performance.

Another aspect of compression though is the mechanism that detects and removes redundancy. There are Static and Dynamic mechanisms mostly in the sense of static and dynamic dictionaries that keep the most frequent patterns for compression. The advantage of a static dictionary is that we can achieve maximum compression for a certain set of patterns, but the downside is that those patterns might be not frequent anymore if the application was profiled with different inputs than

the ones are currently used. Using a dynamic mechanism, that can update its dictionary or create other kind of dynamic correlations between duplicated data, will provide more performance in cases where profiling is not efficient or even cannot be done due to legacy code. The downside of such a mechanism is that it needs more logic to detect the redundancy rather than just probing a dictionary of frequent patterns.

In the next section, we will describe our approach and why we choose it based on the previous work and discussion in this chapter.

### 2.5 Cache Content Duplication (CCD)

We propose Cache Content Duplication (CCD), a phenomenon that appears in the cache and can be exploited by a dynamic hardware mechanism. CCD is defined in Section 1.2.

The key difference of our work from most of the previous effort [43, 23, 44, 45, 49, 50, 52, 55, 56, 57, 53, 54] is that we consider redundancy at the granularity of cache blocks and detect it dynamically using a hardware mechanism instead of comparing arbitrary patterns with profiling aid. Furthermore, most of the previously proposed techniques have static dictionaries or compress only the zero value. We propose the use of a dictionary that is built during execution by dynamically detecting duplicated sequences.

Code compaction [24, 58, 59] and CCD for instruction caches share some similarity since both exploit redundancy in code. However, compaction methods are compiler based whereas the method considered here is dynamic hardware based. The static approach can detect repetition at a coarser scale, for example functions with multiple basic blocks. CCD duplication is limited to at most a cache block at a time. Code compaction typically reduces code size and cache misses, at the expense of increasing the dynamic instruction count. CCD, on the other hand, aims to reduce execution time using extra hardware, instead of extra instructions, to minimize/eliminate

the penalty for misses on duplicated sequences. Furthermore, CCD may be the only way to exploit duplication in legacy code where there is no opportunity for re-optimization.

Few other works attempted to use dynamic mechanisms and dynamic dictionaries to compress the caches like CCD. One of these works is the address correlation [46] which also exploits the duplication of content at different addresses dynamically. Nonetheless, our work is distinct because:

(a) we also consider the duplication of instruction blocks whereas in [46] the focus is individual data values, and (b) we propose hardware mechanisms for detecting and exploiting CCD.

The authors of [47] and [48] propose something similar to our work on Last Level Caches. The approach is the same but the authors of [47] do not provide any performance evaluation of their mechanism and also make many assumptions for the cache to avoid the problem of backward pointers from data to tags when a tag invalidation is needed on data replacements. On the other hand the authors of [48] present a mechanism that is only applicable on buffer caches and cannot be applied in hardware since it requires expensive data structures like very long link lists.

Biswas' work [51] also exploits the CCD phenomenon dynamically as proposed in [12] but only for a specific scenario in which multiple instances of the same application share an L2 cache. Our work extends more by detecting CCD in multiple levels of the memory hierarchy, different granularities and multiprogram workloads with different applications. We also detect CCD within the same application while [51] considers only CCD across multiple instances of an application.

Overall, previous work considered either the compression and compaction of arbitrary length sequences of data or instructions, or the compression at the granularity of individual instructions or values. Our work's major differences from previous are that we combine all the following characteristics:

We propose a dynamic hardware detection mechanism that detects and creates relations

of duplicated content dynamically. This, as opposed to profiling, enables the mechanism

to detect and remove all possible duplication in the cache at the block level and smaller granularities

- The redundancy is detected dynamically without static dictionaries and profiling. The dynamic detection using hash content allows to apply our design to any application and inputs and legacy code

- We detect duplication at block level for various granularities while most of the previous work was focusing on frequent values or whole cache blocks.

- We detect duplication within the same application on a single thread execution and across

different applications on a multiprogram execution. This enables the detection of duplication among similar codes and statically linked libraries.

Table 1 summarizes all previously proposed techniques and their characteristics including their hardware and performance overheads.

Table 1: Summary of related work

| Article         | Granularity          | Algorithm                  | Value range       | Perf. Overhead                                 | Area overhead                        | Cache Level      |

|-----------------|----------------------|----------------------------|-------------------|------------------------------------------------|--------------------------------------|------------------|

|                 |                      |                            | Dynam             | Dynamic Compression                            |                                      |                  |

| Douglis [43]    | Memory Pages         | LZRW1                      | 16KB hash table   | 1                                              | 38KB + 0.8% of memory size           | Main memory      |

| Kjelso [23]     | Memory Pages         | X-Match                    | 1                 | 100MB/sec Compression, 140MB/sec Decompression | 110k gates                           | Main memory      |

| Lefurgy [44]    | Instruction          | Frequent instructions      | 64K instructions  | 75 cycles/compressed block                     | Software Decompression               | Main memory      |

| Zhang [45]      | Word                 | Frequent values            | 7 values          | 0 (Accessed in parallel)                       | 3KB (32KB DMC, 64byte block)         | L1 data cache    |

| Sendag [46]     | Word                 | Dynamic Correlation        | 1                 | 1                                              | 1                                    | L1 data cache    |

| Molina [47]     | Segments             | Dynamic Correlation        | ı                 | ı                                              | 1                                    | L2 cache         |

| Morrey [48]     | Segments             | Dynamic Correlation        | 1                 | 1                                              | 1                                    | Buffer cache     |

| Alameldeen [49] | Patterns             | Frequent Patterns          | 7 patterns        | 5 cycles/compressed block                      | 19bits-counter + Decomp. logic       | L2 cache         |

| Hallnor [50]    | Block segments       | TZSS                       | 1                 | 32 cycles compression, 8 cycles                | 134KB                                | Main memory and  |

|                 |                      |                            |                   | decompression                                  |                                      | L3 cache         |

| Biswas [51]     | Cache blocks         | Same virtual address       | All possible      | 0 (normal cache access)                        | 4.28% of the cache size              | L2 cache         |

| Kjelso [23]     | Memory Pages         | X-RL (Addition to X-Match) | Zeros             | 100MB/sec Compression, 140MB/sec Decompression | 0 (Addition to X-Match)              | Main memory      |

| Villa [52]      | Bytes                | Dynamic detection          | Zeros             | 0 cycles                                       | 1 bit per byte                       | L1 data cache    |